数字设计ic芯片步骤

网站前端开发的关键步骤:

1、规格型号制订

芯片规格型号:芯片必须做到的实际作用和特性层面的规定

2、总体设计

便是依据规格型号规定,执行实际构架,区划控制模块作用。

3、HDL编号

应用硬件配置描述语言(vhdlVeriloghdl)将作用以编码的方式叙述完成。换句话说换句话说将具体的硬件配置电源电路作用根据HDL語言叙述起來,产生RTL编码(应用cadence软件)

4、模拟仿真认证

模拟仿真认证便是检测编号设计方案的准确性,模拟仿真认证专用工具Mentor企业的Modelsim,Synopsys的VCS,也有Cadence的NC-Verilog均能够 对RTL级的编码开展设计方案认证?(应用Cadence或Modelsim或Synopsys的VCS等手机软件)

5、STA

StaticTimingAnalysis(STA),静态数据时序剖析,归属于认证范围,它关键是在时序上对电源电路开展认证,查验电源电路是不是存有创建時间(setuptime)和维持時间(holdtime)的犯规(violation)。一个存储器出現这两个时序犯规时,是没有办法恰当取样数据信息和輸出数据信息的,因此以存储器为基本的数据芯片作用毫无疑问会出現难题。(Synopsys的PrimeTime)

6、方式认证

是认证范围,它是以作用上(STA是时序上)对综合性后的网表开展认证。常见的便是等额的相关检查方式 ,以作用认证后的HDL设计方案为参照,比照综合性后的网表作用,她们是不是在作用上存有等额的性。那样做是以便确保在逻辑性综合性全过程中沒有更改原来HDL叙述的电源电路作用。(方式认证专用工具有Synopsys的Formality)

从设计方案水平上而言,网站前端开发的結果便是获得了芯片的门级网表电源电路

Backenddesignflow后端开发设计流程:

1、DFT

DesignForTest,可测性设计方案。芯片內部通常都内置检测电源电路,DFT的目地便是在设计方案的情况下就考虑到未来的检测。DFT的普遍方式 便是,在设计方案中插进扫描仪链,将非扫描仪模块(如存储器)变成扫描仪模块。有关DFT,一些书本上有详解,对比照片就行了解一点。(DFT专用工具Synopsys的DFTCompiler)

2、合理布局整体规划(FloorPlan)

合理布局整体规划便是置放芯片的宏单元控制模块,在整体上明确各种各样作用电源电路的放置部位,如IP控制模块,RAM,I/O脚位这些。合理布局整体规划能立即危害芯片最后的总面积。(专用工具为Synopsys的Astro)

3、CTS

ClockTreeSynthesis,钟表综合性,通俗一点说便是钟表的走线。因为时钟信号在数据芯片的全局性指挥者功效,它的遍布应该是对称式的连在每个存储器模块,进而使钟表从同一个钟表源抵达每个存储器时,钟表延迟时间差别最少。这也是为什么时钟信号必须独立走线的缘故。CTS专用工具,(Synopsys的PhysicalCompiler)

4、走线(Place&Route)

这儿的走线就是指一般数据信号走线了,包含各种各样标准单元(基础逻辑门电路)中间的布线。例如大家平时听见的0.13um加工工艺,换句话说90nm加工工艺,事实上便是这儿金属材料走线能够 做到的最小宽度,从外部经济上看便是MOS管的沟道长短。(专用工具Synopsys的Astro)

5、寄生参数获取

因为输电线自身存有的电阻器,邻近输电线中间的互感,耦合电容在芯片內部会造成数据信号噪音,串扰和反射面。这种效用会造成信号完整性难题,造成数据信号工作电压起伏和转变,假如比较严重便会造成数据信号失帧不正确。获取寄生参数开展再度的剖析认证,剖析信号完整性难题是十分关键的。(专用工具Synopsys的Star-RCXT)

6、板图物理学认证

对进行走线的物理学板图开展作用和时序上的认证,认证新项目许多 ,如LVS(LayoutVsSchematic)认证,简易说,便是板图与逻辑性综合性后的门级电路原理图的比照认证;DRC(DesignRuleChecking):设计方案标准查验,查验联线间隔,联线总宽等是不是考虑加工工艺规定,ERC(ElectricalRuleChecking):电气设备标准查验,查验短路故障和引路等电气设备标准犯规;这些。专用工具为Synopsys的Hercules具体的后端开发步骤还包含电源电路功能损耗剖析,及其伴随着生产制造加工工艺不断发展造成的DFM(可生产制造性设计方案)难题。物理学板图认证进行也就是全部芯片设计进行。

7、物理学板图以GDSII的格式文件交到芯片代工企业(称之为Foundry)在圆晶硅单晶上作出具体的电源电路,

8、再开展封裝和检测。

注解:(1)VCS是编译程序型Verilog手机模拟器通称VCS.

(2)DesignCompiler为Synopsys企业逻辑性生成专用工具,通称DC

(3)ICCompiler是Synopsys新一代合理布局综合布线系统(Astro是前一代合理布局综合布线系统).通称ICC

(4)PrimeTime是对于繁杂、上百万门芯片开展全芯片、门级静态数据时序剖析的专用工具。通称PT.

(5)HerculesTM能够 开展层次化的物理层认证,以保证板图与芯片的一致性

(6)Star-RCXT是电子设计自动化技术(EDA)行业内寄生参数获取解决方法的金子规范

(7)Synopsys的LEDA是一种可编程控制器代码设计标准查验器,它出示全芯片级混和語言(Verilog和VHDL)解决工作能力,进而加速了繁杂的SOC设计方案的开发设计

(8)Formality是一种等效电路性测试工具,选用方式认证的技术来分辨一个设计方案的2个版本号在作用上是不是等效电路,通称FM.

DRC要认证的目标是板图,大家的板图一般是根据二种方式 获得的。一种是用virtuoso等板图编辑工具手工制作绘图。这在仿真模拟设计方案中比较广泛。另一种是用Cadence的SE等全自动合理布局走线专用工具(APR)由网表文档全自动造成。

水壶

水壶 餐具

餐具 锅具

锅具 刀具

刀具 雨伞

雨伞 衣架

衣架 收纳用品

收纳用品 居家生活

居家生活 灯具

灯具 茶具

茶具 床上用品

床上用品 家居饰品

家居饰品 数据线

数据线 充电器

充电器 充电宝

充电宝 耳机

耳机 鼠标

鼠标 键盘

键盘 蓝牙音箱

蓝牙音箱 电源适配器

电源适配器 车充

车充 转换线

转换线 集线器

集线器 麦克风

麦克风 电视

电视 冰箱

冰箱 空调

空调 洗衣机

洗衣机 电风扇

电风扇 微波炉

微波炉 厨房电器

厨房电器 生活电器

生活电器 衣服

衣服 裤子

裤子 皮带

皮带 饰品

饰品 鞋子

鞋子 袜子

袜子 手提包

手提包 行李箱

行李箱 内衣

内衣 钱包

钱包 帽子

帽子 眼镜

眼镜 办公家具

办公家具 打印机

打印机 放映机

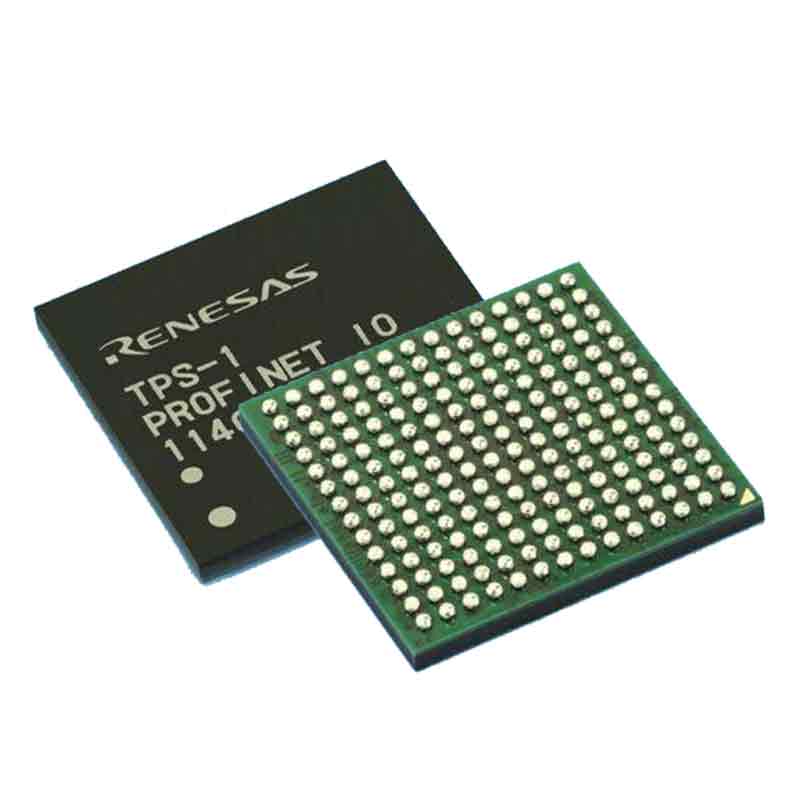

放映机 IC芯片

IC芯片 电容

电容 电阻

电阻 电感

电感 二极管

二极管 三极管

三极管 传感器

传感器 单片机

单片机 存储器

存储器 驱动器

驱动器 晶振

晶振 继电器

继电器 二手电脑

二手电脑 二手设备

二手设备 二手手机

二手手机 电子废料

电子废料 布料

布料 原材料

原材料 废旧电缆

废旧电缆 废铜废铁

废铜废铁 废纸塑料

废纸塑料

需求发布