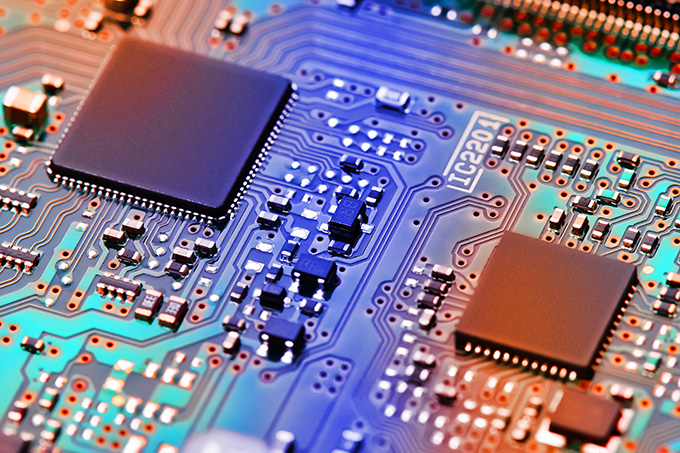

SoC技术有什么作用?科谱IC芯片封裝技术

得到一颗IC芯片要历经从设计方案到生产制造悠长的步骤,殊不知一颗芯片非常小且薄,如果不出外释放维护,会被随便的划伤毁坏。除此之外,由于芯片的规格细微,假如无需一个很大规格的机壳,将不容易以人工服务按置在电路板上。而这个时候封裝技术性就大展身手了,因而,文中接下去要对于封裝多方面叙述详细介绍。

现阶段普遍的封裝有二种,一种是电动玩具车内普遍的,灰黑色有点像大蜈蚣的DIP封裝,另一为选购罐装CPU时普遍的BGA封装。对于别的的封裝法,也有初期CPU应用的PGA(PinGridArray;PinGridArray)或者DIP的改进版QFP(塑胶正方形扁平封装)等。由于有太多种多样封裝法,下列将对DIP及其BGA封装做详细介绍。

传统式封裝,历久不衰

最先要详细介绍的是单双排直立式封裝(DualInlinePackage;DIP),从下面的图能够 见到选用此封裝的IC芯片在单双排接脚底,看上去会像条灰黑色大蜈蚣,令人印象深刻,此封裝法为最开始选用的IC封装技术性,具备成本费便宜的优点,合适中小型且不需接太多段的芯片。可是,由于大多数选用的是塑胶,热管散热实际效果较弱,不能满足现行标准髙速芯片的规定。因而,应用此封裝的,大多数是历久不衰的芯片,如下图中的OP741,或者对运行速率没那麼规定且芯片较小、接孔较少的IC芯片。

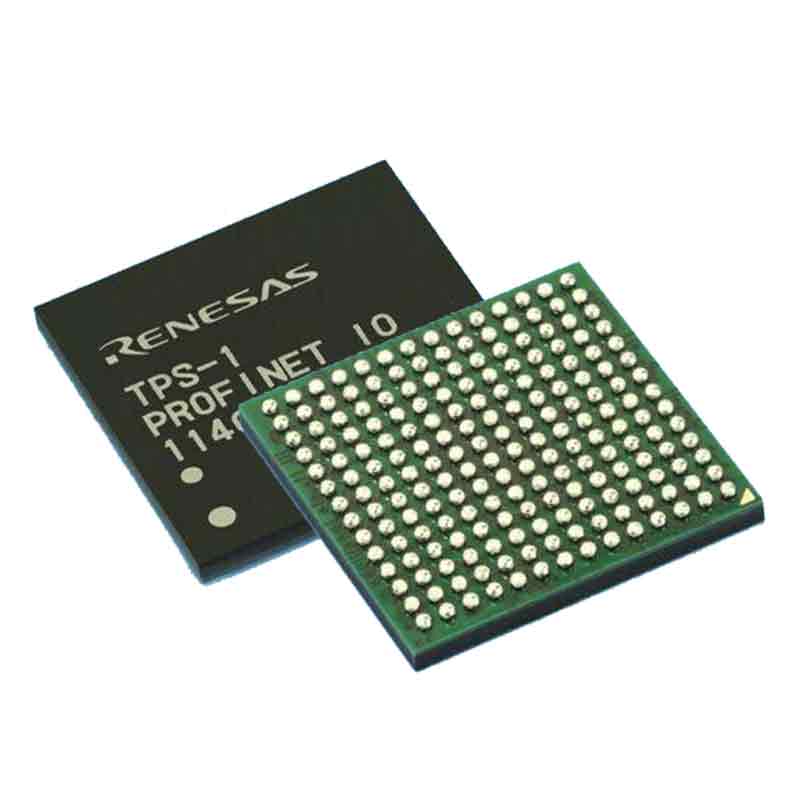

对于球格数组(BallGridArray,BGA)封裝,和DIP对比封裝容积较小,可随便的放进容积较小的设备中。除此之外,由于接脚位在芯片正下方,和DIP对比,可容下大量的金属材料接脚,

非常合适必须较多触点的芯片。殊不知,选用这类封裝法成本费较高且联接的方式 较繁杂,因而大多数用在高价格的商品上。

行動设备盛行,新技术应用迈上演出舞台

殊不知,应用之上这种封裝法,会消耗掉非常大的容积。像如今的行動设备、配戴设备等,必须非常多种多样部件,假如每个部件都单独封裝,组成起來将消耗十分大的室内空间,因而现阶段有二种方式 ,可考虑变小容积的规定,各自为SoC(SystemOnChip)及其SiP(SystemInPacket)。

在全智能手机上刚盛行时,在各种财经杂志上皆可发觉SoC这一专有名词,殊不知SoC到底是什么东西?简易而言,便是将本来不一样作用的IC,融合在一颗芯片中。意谓这一方式 ,不光能够 变小容积,还能够变小不一样IC间的间距,提高芯片的处理速度。对于做法,就是在IC设计方案時间时,将每个不一样的IC放到一起,再通过此前详细介绍的设计流程,制做成一张光罩。

殊不知,SoC并不是只能优势,要设计方案一颗SoC必须非常多的技术性相互配合。IC芯片分别封裝时,都有封裝外界维护,且IC与IC间的间距较远,较为不容易产生互动影响的情况。可是,当将全部IC都包裝在一起时,便是恶梦的刚开始。IC设计方案厂要从原来的单纯性设计方案IC,变为掌握并融合每个作用的IC,提升技术工程师的劳动量。除此之外,也会碰到许多的情况,好像通信芯片的高频率信号将会会危害别的作用的IC等情况。

除此之外,SoC还必须得到别的生产商的IP(intellectualproperty)受权,才可以将他人设计方案好的部件放进SoC中。由于制做SoC必须得到整粒IC的设计方案关键点,才可以制成详细的光罩,这另外也提升了SoC的设计方案成本费。也许会许多人提出质疑为何不自身设计方案一颗就好了呢?由于设计方案各种各样IC必须很多和该IC有关的专业知识,只能像Apple那样金多的公司,才有费用预算能从各大型企业挖人顶级技术工程师,以设计方案一颗全新升级的IC,通过协作受权還是比自主产品研发划得来多了。

折衷方案,SiP亮相

做为取代计划方案,SiP迈上融合芯片的演出舞台。和SoC不一样,它是选购每家的IC,在最后一次封裝这种IC,这般便少了IP受权这一步,大幅度降低设计方案成本费。除此之外,由于他们是分别单独的IC,相互的影响水平大幅度降低。

选用SiP技术性的商品,最知名的非AppleWatch莫属。由于Watch的室内空间很小,它没法选用传统式的技术性,SoC的设计方案成本费又太高,SiP变成主要之选。意谓SiP技术性,不光可变小容积,还可拉进每个IC间的间距,变成行得通的折衷方案。下面的图就是AppleWatch芯片的框架图,能够 见到非常多的IC包括在这其中。

进行封裝后,便要进到检测的环节,在这个环节便要确定封裝完的IC是不是有一切正常的运行,恰当准确无误以后便可交货给组装厂,制成大家所闻的电子设备。到此,半导体产业便完成了全部生产制造的每日任务。

水壶

水壶 餐具

餐具 锅具

锅具 刀具

刀具 雨伞

雨伞 衣架

衣架 收纳用品

收纳用品 居家生活

居家生活 灯具

灯具 茶具

茶具 床上用品

床上用品 家居饰品

家居饰品 数据线

数据线 充电器

充电器 充电宝

充电宝 耳机

耳机 鼠标

鼠标 键盘

键盘 蓝牙音箱

蓝牙音箱 电源适配器

电源适配器 车充

车充 转换线

转换线 集线器

集线器 麦克风

麦克风 电视

电视 冰箱

冰箱 空调

空调 洗衣机

洗衣机 电风扇

电风扇 微波炉

微波炉 厨房电器

厨房电器 生活电器

生活电器 衣服

衣服 裤子

裤子 皮带

皮带 饰品

饰品 鞋子

鞋子 袜子

袜子 手提包

手提包 行李箱

行李箱 内衣

内衣 钱包

钱包 帽子

帽子 眼镜

眼镜 办公家具

办公家具 打印机

打印机 放映机

放映机 IC芯片

IC芯片 电容

电容 电阻

电阻 电感

电感 二极管

二极管 三极管

三极管 传感器

传感器 单片机

单片机 存储器

存储器 驱动器

驱动器 晶振

晶振 继电器

继电器 二手电脑

二手电脑 二手设备

二手设备 二手手机

二手手机 电子废料

电子废料 布料

布料 原材料

原材料 废旧电缆

废旧电缆 废铜废铁

废铜废铁 废纸塑料

废纸塑料

需求发布